## ASSP Communication Control

# **155-Mbps ATM Transceiver**

### MB582A/583A

### DESCRIPTION

The MB582A and MB583A are the chip set that forms a transceiver used for high-speed, point-to-point communications over optical fibers such as in ATM-LAN (asynchronous transfer mode LAN), SDH (synchronous digital hierarchy), and SONET (synchronous optical network).

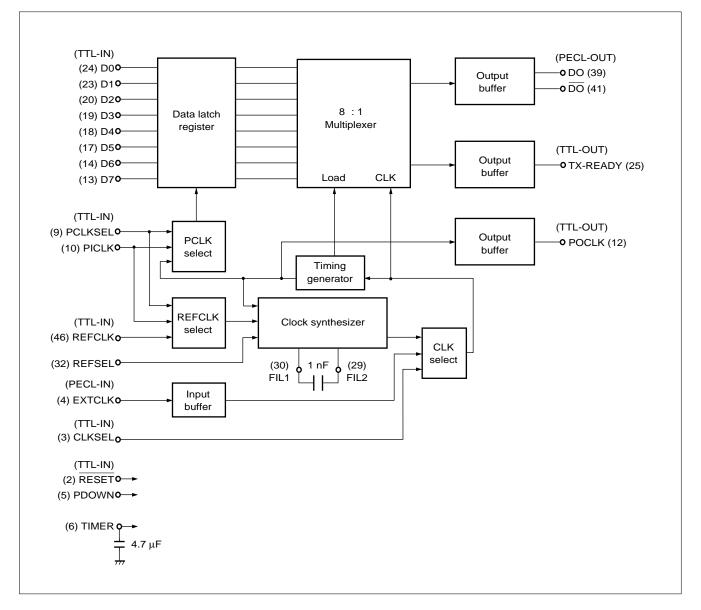

The MB582A transmitter chip generates a high-frequency clock signal from a low-frequency reference clock signal using an internal phase-locked loop (PLL). With the generated clock, the MB582A multiplexes eight-channel parallel data into single-channel serial data.

The MB583A receiver chip extracts and regenerates the regenerated clock signal from received serial data using an internal PLL. With the regenerated clock, the MB583A demultiplexes single-channel serial data into eight-channel parallel data.

### ■ FEATURES

- Applicable to ATM, SDH, and SONET

- 155.52-Mbps serial data transmission

- Internal PLL

- Two reference clocks available (19.44 and 51.84 MHz)

- PECL serial interface plus TTL parallel interface

- Single +5 V power supply

- Directly connectable to ATM network termination controller (MB86683 NTC)

- Power save mode with no signal

- Low power consumption (about 0.3 W), wide operating temperature range (-40°C to +85°C)

- High-speed bipolar technology

| Part number | Function    | Serial data transmission rate | Transmission code | Transmission<br>medium | Power consumption |

|-------------|-------------|-------------------------------|-------------------|------------------------|-------------------|

| MB582A      | Transmitter | 155.52 Mbps                   | NRZ               | Optical, UTP5          | 0.25 W            |

| MB583A      | Receiver    | 155.52 Mbps                   | NRZ               | Optical, UTP5          | 0.3 W             |

### ■ PRODUCT SERIES

### PACKAGE

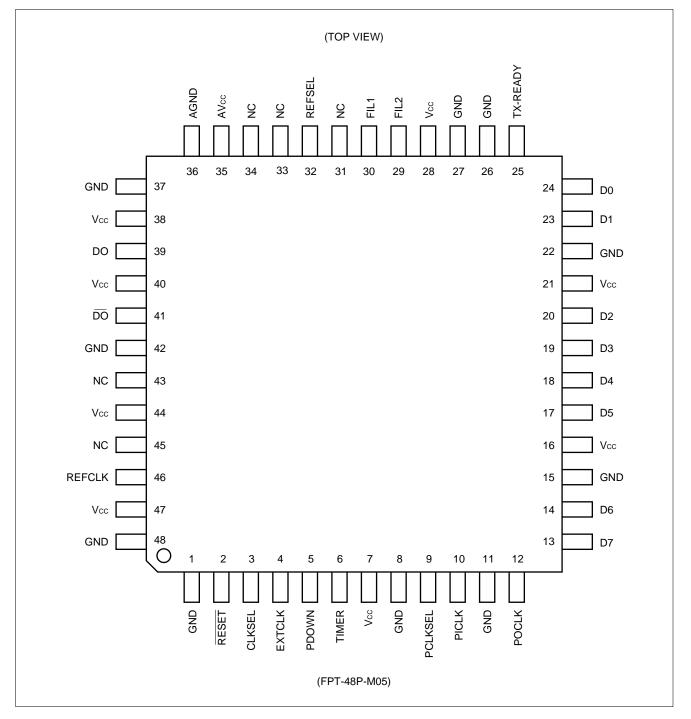

- PIN ASSIGNMENTS

- MB582A (transmitter)

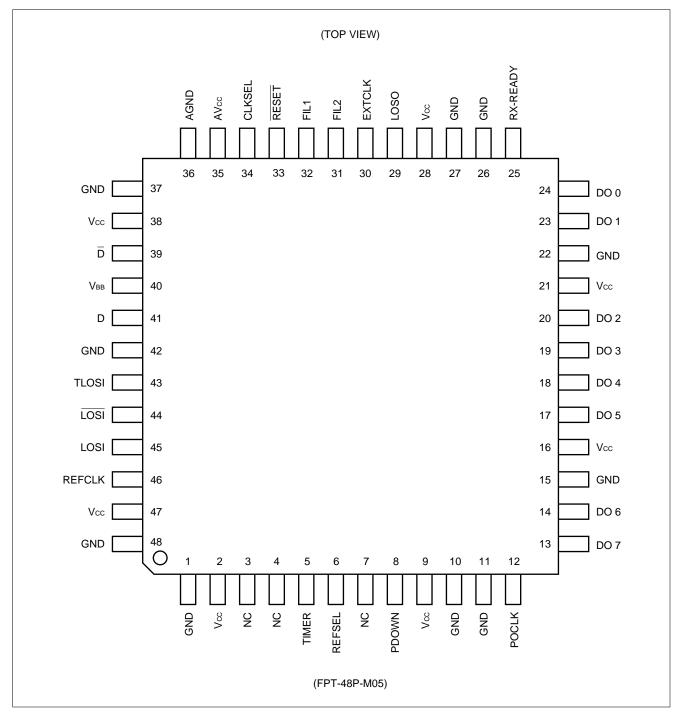

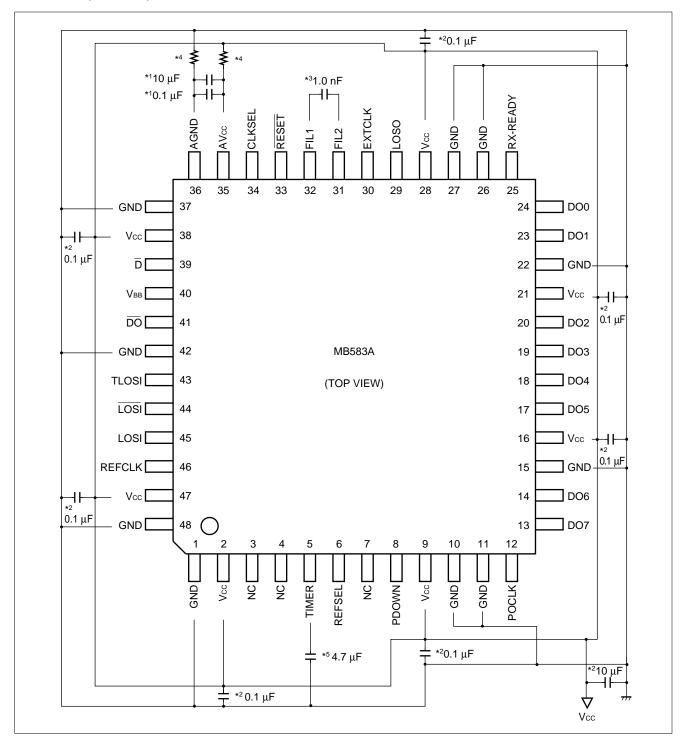

### • MB583A (receiver)

### ■ PIN DESCRIPTION

### • MB582A (Transmitter)

| Pin no.                      | Symbol   | Pin name                        | I/O interface<br>(speed)                       | Function                                                                                                                                                                                                                                                                                                                                                      |  |

|------------------------------|----------|---------------------------------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 24, 23<br>20 to 17,<br>14,13 | D0 to D7 | Parallel data<br>input          | TTL input<br><19.44<br>Mbyte/s>                | <b>Parallel data input pins:</b> Parallel data D0 to D7 are fetched at the rising edge of the PICLK pulse or by the internal parallel clock.                                                                                                                                                                                                                  |  |

| 10                           | PICLK    | Parallel clock<br>input         | TTL input<br><19.44 MHz>                       | <b>Clock input pin for parallel data fetching:</b><br>Parallel data D0 to D7 are fetched at the rising edg<br>of the PICLK pulse. This pin is used for the clock<br>synthesizer. Connect a stable oscillator (such as a<br>crystal oscillator within ±20 ppm) to this pin. This pi<br>is used when PCLKSEL = "0". This pin can't be use<br>when REFSEL = "0". |  |

| 9                            | PCLKSEL  | Parallel clock<br>selection     | TTL input<br><0 or 1>                          | <b>Clock selection pin for parallel data fetching:</b><br>The internal parallel clock and PICLK are selected<br>when this pin inputs "1" and "0," respectively.<br>Also, this pin is used to select the reference clock for<br>the clock synthesizer. REFCLK and PICLK are<br>selected when this pin inputs "1" and "0",<br>respectively.                     |  |

| 46                           | REFCLK   | Reference<br>clock input        | TTL input<br><19.44 or<br>51.84 MHz>           | <b>Reference clock input pin:</b> This pin is used for the PLL circuit in the clock synthesizer. Connect a stable oscillator (such as a crystal oscillator within $\pm 20$ ppm) to this pin.<br>One of two reference clocks can be selected.<br>This pin is used when PCLKSEL = "1".                                                                          |  |

| 32                           | REFSEL   | Reference<br>clock<br>selection | TTL input<br><0 or 1>                          | <b>Reference clock selection pin:</b><br>The 19.44- and 51.84-MHz reference clocks are<br>selected when this pin inputs "1" and "0,"<br>respectively.                                                                                                                                                                                                         |  |

| 4                            | EXTCLK   | External<br>clock input         | PECL input<br><up to<br="">155.52 MHz&gt;</up> | <b>Single PECL input pin:</b> This pin inputs a high-<br>frequency external clock signal to execute an 8-to-1<br>multiplexer function independent of the clock<br>synthesizer.<br>In this case, the operating frequency is free and may<br>be up to 155.52 MHz. This pin is used when<br>CLKSEL = "0".                                                        |  |

(Continued)

| Pin no.  | Symbol   | Pin name                 | I/O interface<br>(speed)         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------|----------|--------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3        | CLKSEL   | Clock<br>selection       | TTL input<br><0 or 1>            | <b>Clock selection pin:</b><br>The clock generated by the clock synthesizer and<br>the EXTCLK clock are selected when this pin inputs<br>"1" and "0," respectively.                                                                                                                                                                                                                                                                                          |

| 2        | RESET    | Reset input              |                                  | Asynchronous reset input pin: This pin is used to<br>initialize the internal state. The internal circuit is<br>reset when this pin inputs "0".<br>Upon reset, the TX-READY and POCLK pins output<br>Low-level signals. Also, the serial data output pins<br>DO and DO output Low- and High-level signals,<br>respectively.<br>The device must be reset when the power is turned<br>on. For details, see "POWER-ON RESET,P17."                                |

| 5        | PDOWN    | Power down               | TTL input<br><0 or 1>            | <b>Sleep mode pin:</b> The circuit supply current is reduced to about 1/3 of normal level when this pin inputs "1." When it inputs "0," the circuit restores normal operation. In sleep mode, the TX-READY and DO pins output Low-level signals; the DO and POCLK pins output High-level signals. For details on sleep mode, see "USING SLEEP MODE, P19."                                                                                                    |

| 39<br>41 |          | Serial data output       | PECL output<br><155.52<br>Mbps>  | <b>Serial data output pins:</b> These pins output NRZ-<br>coded serial data converted from parallel data in the<br>order of D7 to D0.                                                                                                                                                                                                                                                                                                                        |

| 12       | POCLK    | Parallel clock<br>output | TTL output<br><19.94 MHz>        | <b>Parallel clock output pin:</b> This pin outputs a parallel clock synchronized with REFLCK. This output pin can be connected to the controller (MB86683 NTC).                                                                                                                                                                                                                                                                                              |

| 25       | TX-READY | Ready output             | TTL output<br><l h="" or=""></l> | Asynchronous READY output pin:<br>This pin indicates whether the MB582 is ready. The<br>pin outputs the High-level signal when the device is<br>in the ready state.<br>The pin does not indicate the ready state when; the<br>PICLK pulse is not input while PCLKSEL = "0"<br>(selecting PICLK for the parallel clock), RESET = "0"<br>(for reset operation), PDOWN = "1" (for sleep<br>mode), or the PLL circuit in the clock synthesizer is<br>not locked. |

| Pin no.                                          | Symbol       | Pin name           | I/O interface<br>(speed) | Function                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------------------------|--------------|--------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6                                                | TIMER        | Timer              |                          | <b>Timer pin:</b> This pin can be used for automatic<br>power-on reset by connecting a 4.7 $\mu$ F capacitor<br>between this pin and the GND pin. Be sure to leave<br>this pin open when not in use. The device must be<br>reset when the power is turned on. The power-on<br>reset can take place automatically only by<br>connecting the capacitor to this pin. For details, see<br>"POWER-ON RESET, P17." |

| 30<br>29                                         | FIL1<br>FIL2 | External capacitor |                          | <b>External capacitor connection pins:</b> A 1 nF capacitor is connected between these pins. This capacitor is the filter capacitor for the clock synthesizer.                                                                                                                                                                                                                                               |

| 31, 33,<br>34, 43,<br>45                         | NC           | Unused pin         |                          | Leave these pins open.                                                                                                                                                                                                                                                                                                                                                                                       |

| 1, 8,<br>11, 15,<br>22, 26,<br>27, 37,<br>42, 48 | GND          | Digital GND        |                          | <b>Digital GND pins:</b> Connect bypass capacitors between these pins and the digital Vcc pins.                                                                                                                                                                                                                                                                                                              |

| 7, 16,<br>21, 28,<br>38, 40,<br>44, 47           | Vcc          | Digital Vcc        |                          | <b>Digital V</b> <sub>cc</sub> <b>pins:</b> Connect bypass capacitors between these pins and the digital GND pins.                                                                                                                                                                                                                                                                                           |

| 36                                               | AGND         | Analog GND         |                          | Analog GND pin: Connect bypass capacitors between this pin and the AV $_{\rm CC}$ (analog V $_{\rm CC}$ ) pin.                                                                                                                                                                                                                                                                                               |

| 35                                               | AVcc         | Analog Vcc         |                          | <b>Analog V</b> cc <b>pin:</b> Connect bypass capacitors between this pin and the AGND (analog GND) pin.                                                                                                                                                                                                                                                                                                     |

### • MB583A (Receiver)

| Pin no.  | Symbol       | Pin name                        | I/O interface<br>(speed)                       | Function                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|----------|--------------|---------------------------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 41<br>39 | D<br>D       | Serial data<br>input            | PECL input<br><155.52<br>Mbps>                 | Serial data input pins: These pins input NRZ-<br>coded data at 155.52 Mbps.                                                                                                                                                                                                                                                                                                                                                |  |

| 45<br>44 | LOSI<br>LOSI | Loss input                      | PECL input<br><0 or 1>                         | <b>Loss input pins:</b> When $LOSI = "1"$ and $\overline{LOSI} = "0$ ," the input serial data is regarded as being lost; the RX-READY and LOSO pins output Low- and High-<br>level signals, respectively. Since the LOSI and $\overline{LOSI}$ pins are both connected to the reference voltage via an internal high resistor, single input is allowed with either of the pins open. These pins are used when TLOSI = GND. |  |

| 43       | TLOSI        | Loss input                      | TTL input<br><0 or 1>                          | <b>Loss input pin:</b> When this pin inputs "1," the input serial data is regarded as being lost; the LOSO pin outputs the High-level signal. This pin is used when $LOSI = GND$ and $\overline{LOSI} = Open$ .                                                                                                                                                                                                            |  |

| 46       | REFCLK       | Reference<br>clock input        | TTL input<br><19.44 or<br>51.84 MHz>           | <b>Reference clock input pin:</b> This pin is used for the PLL circuit in the clock recovery unit. Connect a stable oscillator (such as a crystal oscillator within $\pm 20$ ppm) to this pin.<br>One of two reference clocks can be selected.                                                                                                                                                                             |  |

| 6        | REFSEL       | Reference<br>clock<br>selection | TTL input<br><0 or 1>                          | <b>Reference clock selection pin:</b><br>The 19.44- and 51.84-MHz reference clocks are<br>selected when this pin inputs "1" and "0,"<br>respectively.                                                                                                                                                                                                                                                                      |  |

| 30       | EXTCLK       | External<br>clock input         | PECL input<br><up to<br="">155.52 MHz&gt;</up> | <b>Single PECL input pin:</b> This pin inputs a high-<br>frequency external clock signal to execute an 1-to-8<br>demultiplexer function independent of the clock<br>recovery unit.<br>In this case, the operating frequency is free and may<br>be up to 155.52 MHz. This pin is used when<br>CLKSEL = "0".                                                                                                                 |  |

| 34       | CLKSEL       | Clock<br>selection              | TTL input<br><0 or 1>                          | <b>Clock selection pin:</b><br>The clock generated by the clock recovery unit and<br>the EXTCLK clock are selected when this pin inputs<br>"1" and "0," respectively.                                                                                                                                                                                                                                                      |  |

| 33       | RESET        | Reset input                     | TTL input<br><0 or 1>                          | Asynchronous reset input pin: This pin is used to<br>initialize the internal state. The internal circuit is<br>reset when this pin inputs "0".<br>Upon reset, the RX-READY, POCLK, and DO0 to<br>DO7 pins output Low-level signals.<br>The device must be reset when the power is turned<br>on. For details, see "POWER-ON RESET,P17."                                                                                     |  |

(Continued)

| Pin no.                        | Symbol        | Pin name                 | I/O interface<br>(speed)         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------|---------------|--------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8                              | PDOWN         | Power down               | TTL input<br><0 or 1>            | Sleep mode pin: When this pin inputs "1," the<br>MB583A enters the sleep mode. Actual sleep<br>operation is performed to reduce the circuit supply<br>current to 1/3 of normal level after serial data input<br>of "0" or "1" remains unchanged, or after a loss<br>signal is received. When a serial data signal is<br>received and the loss signal is cleared, the device<br>restores normal circuit operation. Note that,<br>whenever the serial data input is variable in level<br>without being fixed as "1" or "0", the device will<br>assume that data is being received (the optical<br>module connected to the serial data input may<br>output variable level when the optical signal<br>interrupted).<br>When PDOWN = "0", the device does not enter the<br>sleep mode regardless of the status of the serial<br>data or loss signals.<br>In sleep state, the RX-READY pin outputs the Low-<br>level signal; the LOSO, POCLK, and DO0 to DO7<br>pins output High-level signals.<br>For details on the sleep mode, see "USING SLEEP<br>MODE, P19." |

| 24, 23,<br>20 to 17,<br>14, 13 | DO0 to<br>DO7 | Parallel data output     | TTL output<br><19.44<br>Mbyte/s> | <b>Parallel data output pins:</b> These pins output NRZ-<br>coded parallel data converted from serial data in the<br>order of DO7 to DO0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 12                             | POCLK         | Parallel clock<br>output | TTL output<br><19.44 MHz>        | Parallel clock output pin:<br>This pin outputs a parallel clock synchronized with<br>serial data. This output pin can be connected to the<br>controller (MB86683 NTC).<br>If no serial data is input when PDOWN = "0" (sleep<br>mode off) or a loss signal is received, this pin serves<br>as a parallel clock output synchronized with<br>REFCLK.<br>If no serial data is input when PDOWN is "1" (sleep<br>mode on) or a loss signal is received, the device<br>enters the sleep state and this pin outputs the High-<br>level signal.<br>Note that, whenever the serial data input is variable<br>in level without being fixed as "1" or "0," the device<br>will assume that data is being received (the optical<br>module connected to the serial data input may<br>output variable level when the optical signal<br>interrupted).                                                                                                                                                                                                                      |

(Continued)

| Pin no.  | Symbol       | Pin name                    | I/O interface<br>(speed)         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------|--------------|-----------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 29       | LOSO         | Loss output                 | TTL output<br><l h="" or=""></l> | Asynchronous Loss output pin: This pin outputs<br>the High-level signal after serial data input of "0" or<br>"1" remains unchanged or on reception of a loss<br>signal.<br>Note that, whenever the serial data input is variable<br>in level without being fixed as "1" or "0," the device<br>will assume that data is being received (the optical<br>module connected to the serial data input may<br>output variable level when the optical signal<br>interrupted).<br>This output pin can be connected to the controller<br>(MB86683 NTC). |

| 25       | RX-READY     | Ready output                | TTL output<br><l h="" or=""></l> | Asynchronous READY output pin: This pin<br>indicates whether the MB583A is ready. The pin<br>outputs the High-level signal when the device is in<br>the ready state.<br>The pin does not indicate the ready state when;<br>serial data input of "0" or "1" remains unchanged, on<br>reception of a loss signal, RESET = "0," or the PLL<br>circuit in the clock recovery unit is not locked.                                                                                                                                                  |

| 40       | VBB          | Reference<br>voltage output |                                  | <b>Reference voltage output pin:</b> For single input of serial data, connect the VBB and $\overline{D}$ pins using a resistor. For differential input of serial data, leave this pin open.                                                                                                                                                                                                                                                                                                                                                   |

| 5        | TIMER        | Timer                       |                                  | <b>Timer pin:</b> This pin can be used for automatic<br>power-on reset by connecting a 4.7 $\mu$ F capacitor<br>between this pin and the GND pin. Be sure to leave<br>this pin open when not in use. The device must be<br>reset when the power is turned on. The power-on<br>reset can take place automatically only by<br>connecting the capacitor to this pin. For details, see<br>"POWER-ON RESET, P17."                                                                                                                                  |

| 32<br>31 | FIL1<br>FIL2 | External capacitor          |                                  | <b>External capacitor connection pins:</b> A 1 nF capacitor is connected between these pins. This capacitor is the filter capacitor for the clock recovery.                                                                                                                                                                                                                                                                                                                                                                                   |

| 3, 4, 7  | NC           | Unused pin                  |                                  | Leave these pins open.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Pin no.                                           | Symbol | Pin name    | I/O interface<br>(speed) | Function                                                                                                           |

|---------------------------------------------------|--------|-------------|--------------------------|--------------------------------------------------------------------------------------------------------------------|

| 1, 10,<br>11, 15,<br>22, 26,<br>27, 37,<br>42, 48 | GND    | Digital GND |                          | <b>Digital GND pins:</b> Connect bypass capacitors between these pins and the digital Vcc pins.                    |

| 2, 9, 16,<br>21, 28,<br>38, 47                    | Vcc    | Digital GND |                          | <b>Digital V</b> <sub>cc</sub> <b>pins:</b> Connect bypass capacitors between these pins and the digital GND pins. |

| 36                                                | AGND   | Analog GND  |                          | <b>Analog GND pin:</b> Connect bypass capacitors between this pin and the AVcc (analog Vcc) pin.                   |

| 35                                                | AVcc   | Analog Vcc  |                          | <b>Analog V</b> cc <b>pin:</b> Connect bypass capacitors between this pin and the AGND (analog GND) pin.           |

### BLOCK DIAGRAMS

### • MB582A (Transmitter)

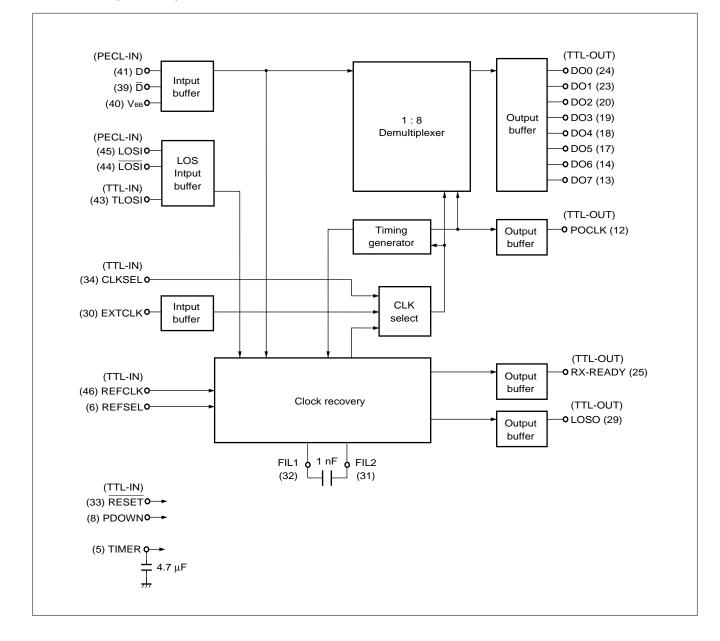

#### • MB583A (Receiver)

### ■ FUNCTIONS

### (1) MB582A (Transmitter)

### Reference clock function

| PCLKSEL  | REFSEL         | Reference clock terminal | Reference clock frequency |

|----------|----------------|--------------------------|---------------------------|

| 1 (OPEN) | 1 (OPEN)       | REFCLK                   | 19.44 MHz                 |

| I (OPEN) | 0              | REFCLK                   | 51.84 MHz                 |

| 0        | 1 (OPEN) PICLK |                          | 19.44 MHz                 |

| 0        | 0              | Prohibit                 |                           |

#### • High-frequency clock function

| CLKSEL   | SEL Internal clock |  | RESET    | Reset |

|----------|--------------------|--|----------|-------|

| 1 (OPEN) | Clock synthesizer  |  | 1 (OPEN) |       |

| 0        | EXTCLK             |  | 0        | Reset |

#### • Parallel clock function

| PCLKSEL  | Parallel data input clock                                                     |  |  |  |

|----------|-------------------------------------------------------------------------------|--|--|--|

| 1 (OPEN) | Internal parallel clock (setup/hold time required between POCLK and D0 to D7) |  |  |  |

| 0        | PICLK (setup/hold time required between PICLK and D0 to D7)                   |  |  |  |

### Sleep mode function

#### • Ready signal function

Reset function

| PDOWN    | Sleep mode |  | TX-READY | Device state |

|----------|------------|--|----------|--------------|

| 1        | Sleep      |  | Н        | Ready        |

| 0 (OPEN) | Wake-up    |  | L        | Not ready    |

The device is not ready when;

- PICLK is not input while PCLKSEL = "0" (selecting PICLK as parallel clock input)

- $\overline{\text{RESET}}$  = "0" (reset operation)

- PDOWN = "1" (sleep state)

- The PLL circuit in the clock synthesizer is not locked (because of the REFCLK frequency not matched, external resistor not connected, etc.)

### • PDOWN and RESET functions

| PDOWN | RESET | Sleep mode | TX-READY | DO               | DO               | POCLK            |

|-------|-------|------------|----------|------------------|------------------|------------------|

| 1     | Х     | Sleep      | L        | L                | Н                | Н                |

| 0     | 1     | Not sleep  | Н        | Normal operation | Normal operation | Normal operation |

|       | 0     |            | L        | L                | Н                | L                |

X: 0 or 1

### (2) MB583A (Receiver)

#### • Reference clock function

| REFSEL   | REFCLK    |

|----------|-----------|

| 1 (OPEN) | 19.44 MHz |

| 0        | 51.84 MHz |

### Reset function

| RESET    | Reset |

|----------|-------|

| 1 (OPEN) | _     |

| 0        | Reset |

### • Loss function

| LOSO | Input serial data |  |  |

|------|-------------------|--|--|

| Н    | Los detection     |  |  |

| L    | Receive state     |  |  |

| LOSI, TLOSI | Input serial data |

|-------------|-------------------|

| 1           | Los detection     |

| 0           | Receive state     |

| Loss signal selection | Setting conditions                       |

|-----------------------|------------------------------------------|

| LOSI, LOSI (PECL)     | TLOSI = GND (OPEN)                       |

| TLOSI (TTL)           | $LOSI = GND also \overline{LOSI} = OPEN$ |

LOSO = H when;

- LOSI or TLOSI = "1"

- Input serial data of "0" or "1" remains unchanged.\*

- \* : Note that, whenever the serial data input is variable in level without being fixed as "0" or "1," the device will assume that data is being received (the optical module connected to the serial data input may output variable level when the optical signal interrupted).

### High-frequency clock function

| CLKSEL   | Internal clock |

|----------|----------------|

| 1 (OPEN) | Clock recovery |

| 0        | EXTCLK         |

#### • Sleep mode function

| PDOWN    | Sleep mode     |

|----------|----------------|

| 1 (OPEN) | Sleep mode ON  |

| 0        | Sleep mode OFF |

The sleep mode is turned on when;

• Input serial data of "0" or "1" remains unchanged.\*

• The loss signal is received.

The device is not ready when;

• Input serial data of "0" or "1" remains unchanged.\*

- The loss signal is received.

- RESET = "0" (reset operation)

- The PLL circuit in the clock recovery unit is not locked (because of the REFCLK frequency not matched, external resistor not connected, etc.)

### • Input serial data, PDOWN, RESET, LOSI, and TLOSI functions

| Input<br>serial data | PDOWN | RESET | LOSI,<br>TLOSI | Sleep mode | RX-READY | LOSO | DO0 to DO7       | POCLK                           |

|----------------------|-------|-------|----------------|------------|----------|------|------------------|---------------------------------|

|                      |       |       | 1              | Sleep      | L        | Н    | Н                | Н                               |

|                      | 1     | 1     | 0              | Not sleep  | Н        | L    | Normal operation | Normal operation                |

|                      |       | 0     | 1              | Sleep      | · L      | Н    | Н                | Н                               |

|                      |       | 0     | 0              | Not sleep  |          | L    | L                | L                               |

| Receive<br>state     | 0     | 1     | 1              | Not sleep  | L        | Н    | Undefined        | Synchronizing<br>with<br>REFCLK |

|                      |       | 0     | 0              |            | Н        | L    | Normal operation | Normal operation                |

|                      |       |       | 1              |            | L        | Н    | 1                | L                               |

|                      |       |       | 0              | L          | L        |      |                  |                                 |

|                      | 1     | Х     | Х              | Sleep      | L        | Н    | Н                | Н                               |

| Loss state           | 0     | 1     | х              | Not sleep  | L        | н    | Undefined        | Synchronizing<br>with<br>REFCLK |

|                      |       | 0     |                |            |          |      | L                | L                               |

Loss state: Input serial data of "0" or "1" remains unchanged.\*

X: 0 or 1

\* : Note that, whenever the serial data input is variable in level without being fixed as "0" or "1," the device will assume that data is being received (the optical module connected to the serial data input may output variable level when the optical signal interrupted).

#### • Ready signal function

| RX-READY | Device state |

|----------|--------------|

| Н        | Ready        |

| L        | Not ready    |

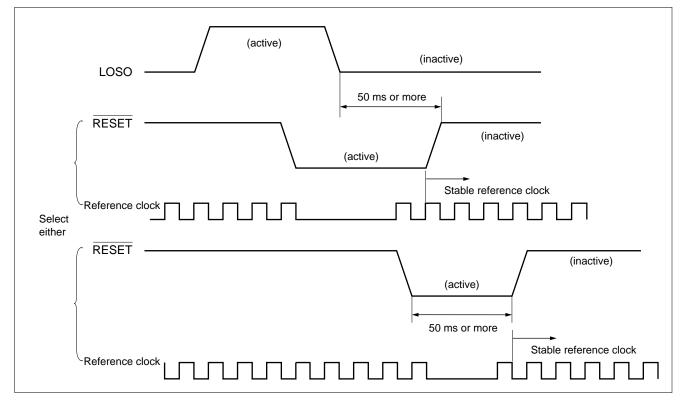

### POWER-ON RESET

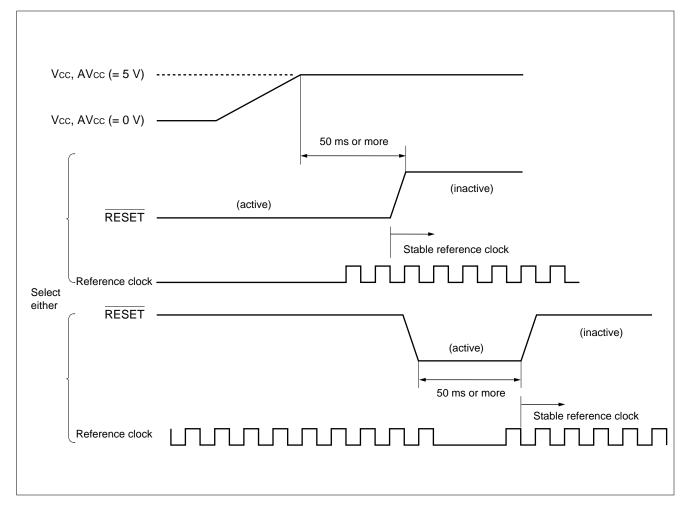

The MB582A and MB583A must be reset when the power is turned on. There are two methods available for resetting each device at power-on. Select the best method.

(1) Apply a reset to the device at power-on, then cancel the reset 50 ms after the V<sub>cc</sub> and AV<sub>cc</sub> have reached 5 V or input a reset pulse with a width of 50 ms after they reached 5 V. Note that a stable reference clock signal (REFCLK or PICLK) must be input before the reset is canceled. (See the diagram below.)

This method eliminates the need for connecting an external capacitor to the TIMER pin as described in method (2).

Be sure to leave the TIMER pin open when not in use.

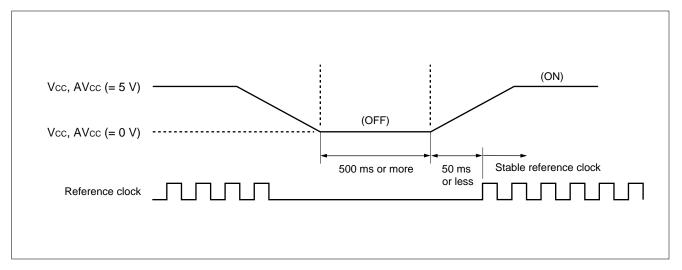

(2) Connect a 4.7  $\mu$ F external capacitor between the TIMER and GND pins. The capacitor is used for automatic power-on reset.

Whenever the power is recycled, ensure that it remains off for at least 500 ms. (See the diagram below.) This method allows the  $\overrightarrow{\text{RESET}}$  signal to be used without considering the restrictions described in method (1). The  $\overrightarrow{\text{RESET}}$  pin may be left open.

Note, however, that a stable reference clock signal (REFCLK or PICLK) must be input within 50 ms after poweron.

### ■ USING SLEEP MODE

### • Using the MB582A Sleep Mode

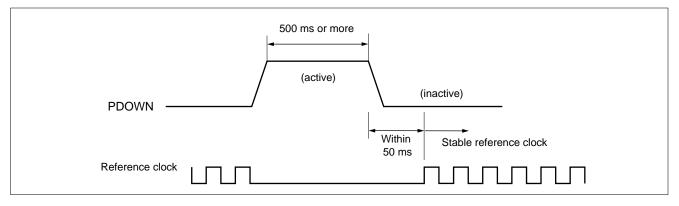

It is necessary to follow either method (1) or (2) when using the sleep mode, otherwise the device will not return to normal operating status.

(1) Apply a reset to the device when it enters sleep mode, then cancel the reset 50 ms after clearing the PDOWN signal or input a reset pulse with a width of 50 ms after clearing the PDOWN signal. Note that a stable reference clock signal (REFCLK or PICLK) must be input before the reset is canceled. (See the diagram below.) This method eliminates the need for connecting an external capacitor to the TIMER pin as described in method (2).

(active) (inactive) **PDOWN** 50 ms or more RESET (inactive) (active) Stable reference clock Reference clock Select either RESET (inactive) (active) 50 ms or more Stable reference clock Reference clock

Be sure to leave the TIMER pin open when not in use.

(2) Connect a 4.7 µF external capacitor between the TIMER and GND pins. The capacitor is used for automatically resetting the sleep mode.

Be sure that the PDOWN signal has an active phase of at least 500 ms. (See the diagram below.)

This method allows the  $\overline{\text{RESET}}$  signal to be used without considering the restrictions described in method (1). The  $\overline{\text{RESET}}$  pin may be left open.

Note, however, that a stable reference clock signal (REFCLK or PICLK) must be input within 50 ms after the power save mode is canceled (as shown in the following illustration.)

### Using the MB583A Sleep Mode

It is necessary to use method (1) when using the sleep mode, otherwise the device will not return to normal operating status.

(1) Apply a reset to the device when the LOSO output goes high (the LOS state detected), then cancel the reset 50 ms after the LOSO output goes low (receive state) or input a reset pulse with a width of 50 ms after the LOSO output changes from high to low. Note that a stable reference clock signal (REFCLK) must be input before the reset is canceled. (See the diagram below.)

Be sure to leave the TIMER pin open when not in use.

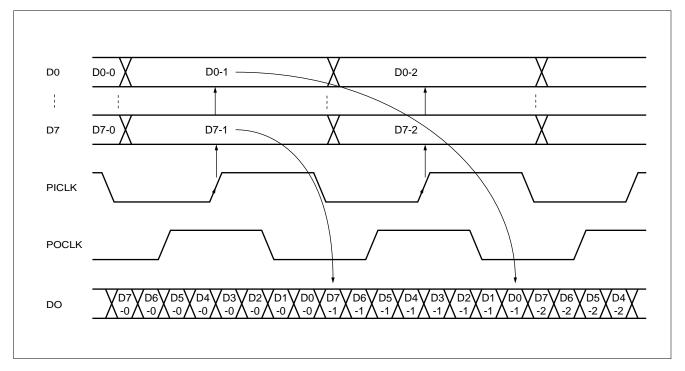

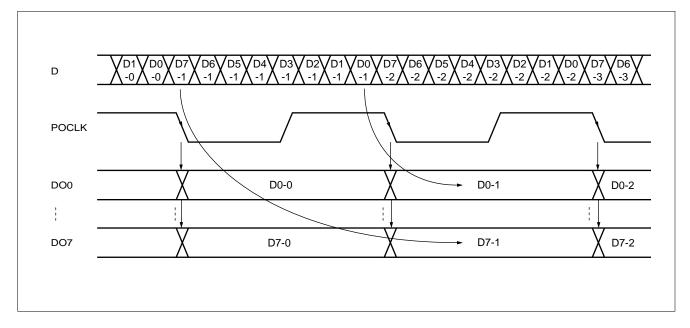

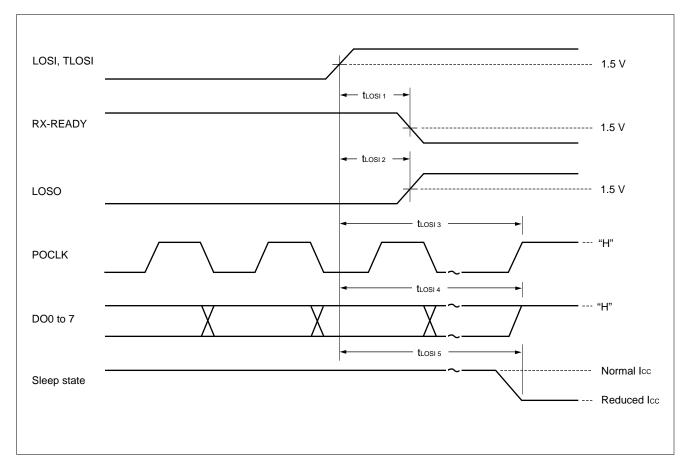

- TIMING CHARTS

- MB582A (Transmitter)

• MB583A (Receiver)

### ■ ABSOLUTE MAXIMUM RATINGS

| Parameter             | Symbol | Rating | Unit            |    |

|-----------------------|--------|--------|-----------------|----|

| Power supply voltage* |        | Vcc    | 0 to 6.0        | V  |

| Input voltage*        | TTL    | Vin    | –0.5 to Vcc+0.5 | V  |

| Input voltage*        | PECL   | Vin    | 2.0 to Vcc      | V  |

| Output voltage*       | TTL    | Vout   | -0.5 to 5.5     | V  |

| Output current        | PECL   | Іоит   | -50             | mA |

| Storage temperature   |        | Tstg   | -55 to +150     | °C |

\* : The voltage is based on GND.

Note: Permanent device damage may occur if the above Absolute Maximum Ratings are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields. However, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit.

### ■ RECOMMENDED OPERATING CONDITIONS

| Parameter                 | Symbol   | Value | Unit       |    |

|---------------------------|----------|-------|------------|----|

| Power supply voltage*     |          | Vcc   | 5.0 ±5 %   | V  |

| High-level output current |          | Іон   | -1         | mA |

| Low-level output current  |          |       | 4          | mA |

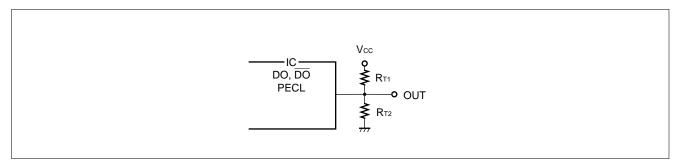

| DO and DO output          | PECL—Vcc | RT1   | 82         | Ω  |

| termination resistors     | PECL—GND | RT2   | 130        | Ω  |

| Operating temperature     |          | Та    | -40 to +85 | °C |

\* : The voltage is based on GND.

#### Connection diagram of PECL output termination resistor

### ELECTRICAL CHARACTERISTICS

### 1. DC Characteristics

• MB582A (transmitter)

(Vcc = +5.0 V ±5.0 %, Ta = -40°C to +85°C)

| De                               |                                    | Cumbal | Cond                                  | 4:ene       |             | Value      |             | Unit |

|----------------------------------|------------------------------------|--------|---------------------------------------|-------------|-------------|------------|-------------|------|

| ra                               | rameter                            | Symbol | Condi                                 | tions       | Min.        | Typ.⁺¹     | Max.        | Unit |

|                                  | High-level input voltage           | Vін    | _                                     | _           | 2.0         | _          | _           | V    |

|                                  | Low-level input voltage            | VIL    |                                       | _           | _           | —          | 0.8         | V    |

| TTL input                        | Input clamp<br>voltage             | Vic    | Vcc = 4.75 V,                         | lı = −18 mA | -1.5        | _          |             | V    |

|                                  | High-level input<br>current        | Ін     | Vcc = 5.25 V,                         | Vı = 2.4 V  | _           | _          | 500         | μΑ   |

|                                  | Low-level input<br>current         | lı.    | Vcc = 5.25 V,                         | Vı = 0.5 V  | -500        |            |             | μA   |

|                                  | High-level<br>output voltage       | Vон    | Vcc = 4.75 V,                         | Іон = –1 mA | 2.4         | _          | _           | V    |

| TTL output                       | Low-level output voltage           | Vol    | Vcc = 4.75 V,                         | lo∟ = 4 mA  |             | —          | 0.5         | V    |

|                                  | Output short-<br>circuit current*2 | los    | Vcc = 5.25 V,                         | Vo = 0 V    | -150        | _          | _           | mA   |

|                                  | High-level input voltage           | Vін    | _                                     | -           | Vcc – 1.165 | _          | Vcc – 0.72  | V    |

|                                  | Low-level input voltage            | VIL    | _                                     | _           | Vcc – 1.95  |            | Vcc – 1.475 | V    |

| Single<br>PECL input<br>(EXTCLK) | High-level input<br>current        | Ін     | $V_I = V_{CC} - 0.7$                  | 2 V         | _           | _          | 200         | μΑ   |

| (                                | Low-level input current            | ١ı     | Vi = Vcc - 1.9                        | 95 V        | -200        | _          |             | μΑ   |

|                                  | Input open-circuit<br>voltage      | Vio    | _                                     | -           | Vcc – 1.26  | Vcc – 1.32 | Vcc – 1.38  | V    |

|                                  |                                    |        |                                       | Ta = -40°C  | Vcc – 1.15  | _          | Vcc - 0.89  | V    |

| PECL                             |                                    |        | Output load:                          | Ta = 0°C    | Vcc – 1.09  |            | Vcc – 0.84  | V    |

| output                           | High-level<br>output voltage       | Vон    | 82 $\Omega$ to Vcc<br>130 $\Omega$ to | Ta = +25°C  | Vcc - 1.05  | Vcc - 0.92 | Vcc - 0.81  | V    |

| (DO, <u>DO</u> )                 | ouipui voitage                     |        | GND 1                                 | Ta = +75°C  | Vcc - 0.99  |            | Vcc - 0.735 | V    |

|                                  |                                    |        |                                       | Ta = +85°C  | Vcc - 0.98  |            | Vcc – 0.72  | V    |

\*1: Typical values assume that Vcc = +5.0 V and Ta = +25°C.

\*2: The output short-circuit duration must not exceed 1 second. More than one output must not be short-circuited at the same time.

(Continued)

| Ba                             | rameter                  | Symbol | Conditions                     |                                                    |            |            | Unit        |    |

|--------------------------------|--------------------------|--------|--------------------------------|----------------------------------------------------|------------|------------|-------------|----|

| Га<br>                         | lametei                  | Symbol | Conu                           | Conditions                                         |            | Typ.⁺¹     | Max.        |    |

|                                |                          |        |                                | Ta = -40°C                                         | Vcc – 1.15 |            | Vcc – 1.63  | V  |

| PECL                           |                          |        | Output load:                   | Ta = 0°C                                           | Vcc – 1.09 |            | Vcc – 1.63  | V  |

| LOW-                           | Low-level output voltage | Vol    | 82 Ω to Vcc<br>130 Ω to        | Ta = +25°C                                         | Vcc – 1.05 | Vcc – 0.92 | Vcc – 1.63  | V  |

|                                |                          |        | GND                            | Ta = +75°C                                         | Vcc - 0.99 |            | Vcc – 1.60  | V  |

|                                |                          |        |                                | Ta = +85°C                                         | Vcc – 0.98 |            | Vcc – 1.595 | V  |

| Supply                         | During operation         | Icc    | Vcc = 5.25 V,                  | I/O = Open                                         |            | 50         | 80          | mA |

| Supply<br>current              | Sleep state              | Ісср   |                                | Vcc = 5.25 V, PDOWN = "1"<br>Other I/O pins = Open |            | 15         | 40          | mA |

| PECL                           | During operation         | lo1    | Vcc = 5.25 V                   |                                                    | -35        | -24        | _           | mA |

| output<br>current<br>(DO + DO) | Sleep state              | IOD1   | Output load: 8<br>130 Ω to GNI |                                                    | -35        | -24        |             | mA |

\* : Typical values assume that Vcc = +5.0 V and Ta = +25°C.

• MB583A (receiver)

(Vcc = +5.0 V ±5.0 %, Ta = −40°C to +85°C)

| -                               |                                                | 0      |                                                           |             | Value      |             |      |  |

|---------------------------------|------------------------------------------------|--------|-----------------------------------------------------------|-------------|------------|-------------|------|--|

| Ра                              | rameter                                        | Symbol | Conditions                                                | Min.        | Typ.*¹     | Max.        | Unit |  |

|                                 | High-level input voltage                       | Vін    | _                                                         | 2.0         |            |             | V    |  |

|                                 | Low-level input voltage                        | VIL    | _                                                         | _           |            | 0.8         | V    |  |

| TTL input                       | Input clamp<br>voltage                         | Vic    | $V_{CC} = 4.75 V$ , $I_{I} = -18 mA$                      | -1.5        |            |             | V    |  |

|                                 | High-level input<br>current                    | Ін     | $V_{CC} = 5.25 \text{ V}, \text{ V}_{I} = 2.4 \text{ V}$  | _           |            | 500         | μA   |  |

|                                 | Low-level input current                        | ١L     | $V_{CC} = 5.25 \text{ V}, \text{ V}_{I} = 0.5 \text{ V}$  | -500        |            |             | μA   |  |

|                                 | High-level<br>output voltage                   | Vон    | $V_{CC} = 4.75 \text{ V}, \text{ I}_{OH} = -1 \text{ mA}$ | 2.4         | _          | _           | V    |  |

| TTL output                      | Low-level output voltage                       | Vol    | Vcc = 4.75 V, Io∟ = 4 mA                                  | _           |            | 0.5         | V    |  |

| c                               | Output short-<br>circuit current <sup>*2</sup> | los    | Vcc = 5.25 V, Vo = 0 V                                    | -150        |            |             | mA   |  |

|                                 | High-level input voltage                       | Vін    | _                                                         | _           |            | Vcc – 0.72  | V    |  |

| Differential                    | Low-level input voltage                        | VIL    | _                                                         | Vcc – 1.95  |            |             | V    |  |

| PECL input<br>(D, D,<br>LOSI,   | Differential input voltage                     | Vdif   | VIH-VIL                                                   | 0.1         |            | 1.2         | V    |  |

| LOSI)                           | High-level input<br>current                    | Ін     | $V_{I} = V_{CC} - 0.72 V$                                 |             |            | 200         | μΑ   |  |

|                                 | Low-level input<br>current                     | ١ı     | $V_{I} = V_{CC} - 1.95 V$                                 | -200        |            |             | μA   |  |

|                                 | High-level input voltage                       | Vін    | —                                                         | Vcc – 1.165 |            | Vcc – 0.72  | V    |  |

| Single                          | Low-level input voltage                        | VIL    |                                                           | Vcc – 1.95  |            | Vcc – 1.475 | V    |  |

| PECL input<br>(EXTCLK,<br>LOSI, | High-level input current                       | Ін     | $V_{I} = V_{CC} - 0.72 V$                                 | _           |            | 200         | μA   |  |

| LOSI)                           | Low-level input<br>current                     | II.    | $V_{I} = V_{CC} - 1.95 V$                                 | -200        |            | _           | μA   |  |

|                                 | Input open-circuit<br>voltage                  | Vio    |                                                           | Vcc – 1.26  | Vcc – 1.32 | Vcc – 1.38  | V    |  |

\*1: Typical values assume that Vcc = +5.0 V and Ta = +25°C.

\*2: The output short-circuit duration must not exceed 1 second. More than one output must not be short-circuited at the same time.

(Continued)

| Parameter              |                      | Symbol Conditions |                                                                        |            | Unit       |            |    |  |

|------------------------|----------------------|-------------------|------------------------------------------------------------------------|------------|------------|------------|----|--|

| Г а                    | Farameter Sym        |                   | Conditions                                                             | Min.       | Typ.*1     | Max.       |    |  |

| V <sub>BB</sub> output | Reference<br>voltage | VBB               | _                                                                      | Vcc – 1.26 | Vcc – 1.32 | Vcc – 1.38 | V  |  |

|                        | During operation     | Icc               | $V_{CC} = 5.25 \text{ V}, \text{PDOWN} = "0"$<br>Other I/O pins = Open |            | 60         | 110        | mA |  |

| Supply current         | Sleep state          | Ісср              | Vcc = 5.25 V, PDOWN = "0"<br>Other I/O pins = Open                     |            | 20         | 50         | mA |  |

\* : Typical values assume that Vcc = +5.0 V and Ta = +25°C.

### 2. AC Characteristics

### (1) MB582A (transmitter)

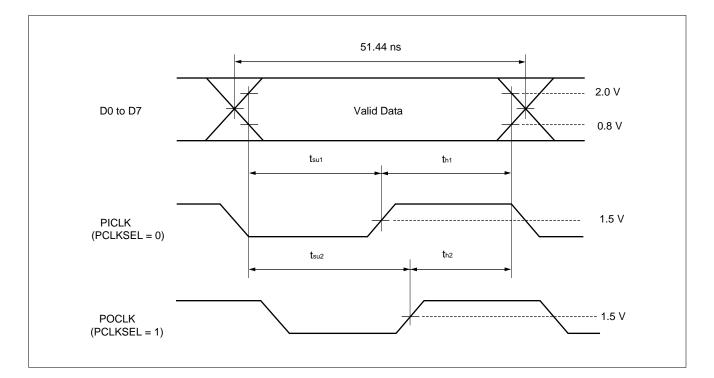

• Parallel clock input and parallel data input timings

(Vcc = +5.0 V ±5.0 %, Ta = −40°C to +85°C)

| Parameter                        |            | Symbol           | Conditions    |      | Unit |      |      |

|----------------------------------|------------|------------------|---------------|------|------|------|------|

|                                  |            |                  |               | Min. | Тур. | Max. | Unit |

| PICLK $\leftrightarrow$ D0 to D7 | Setup time | t <sub>su1</sub> | PCLKSEL = "0" | 5.0  |      |      | ns   |

|                                  | Hold time  | th1              |               | 5.0  | _    | _    | ns   |

| POCLK $\leftrightarrow$ D0 to D7 | Setup time | t <sub>su2</sub> | PCLKSEL = "1" | 5.0  | —    | _    | ns   |

| POCLK $\leftrightarrow$ D0 to D7 | Hold time  | th2              | FOLKSEL = 1   | 5.0  |      |      | ns   |

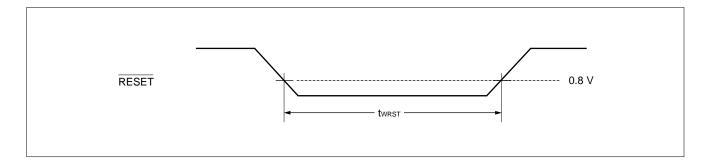

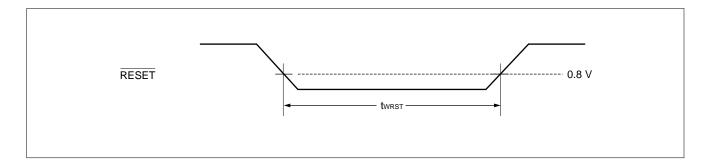

### • Reset input pulse width

### $(V_{CC} = +5.0 \text{ V} \pm 5.0 \text{ \%}, \text{Ta} = -40^{\circ}\text{C to } +85^{\circ}\text{C})$

| Parameter |           | Symbol      | Symbol Conditions | Value         |  |      | Unit |

|-----------|-----------|-------------|-------------------|---------------|--|------|------|

|           | Farameter | Symbol      | Conditions        | Min. Typ. Max |  | Max. | Unit |

| RESET     | Pulse     | width twrst | —                 | 100           |  |      | ns   |

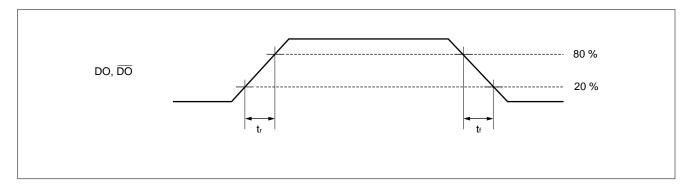

### • PECL output waveform

### $(V_{CC} = +5.0 \text{ V} \pm 5.0 \text{ \%}, \text{Ta} = -40^{\circ}\text{C to } +85^{\circ}\text{C})$

| Parameter |           | Symbol Conditions |                                                                       |      | Unit  |      |      |

|-----------|-----------|-------------------|-----------------------------------------------------------------------|------|-------|------|------|

|           |           |                   |                                                                       | Min. | Тур.* | Max. | Onit |

|           | Rise time | tr                | 20 % -80 %                                                            |      | 0.7   |      | ns   |

| DO, DO    | Fall time | tr                | Output load:<br>82 $\Omega$ to V <sub>CC</sub><br>130 $\Omega$ to GND |      | 0.7   |      | ns   |

\* : Typical values assume that Vcc = +5.0 V and Ta = +25  $^\circ\text{C}.$

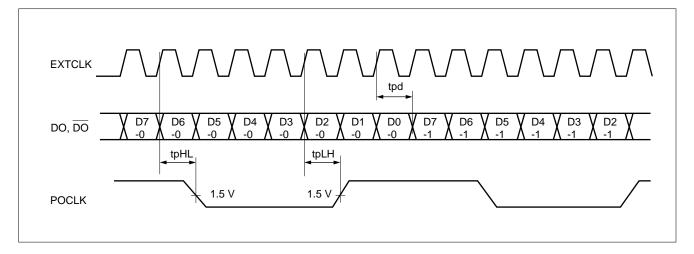

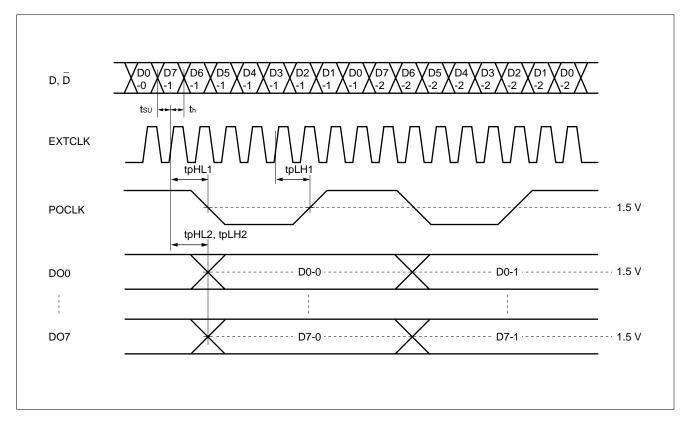

• External serial clock input timing

| Baramata                        | -     | Symbol | Conditions   |      | Unit  |      |      |  |

|---------------------------------|-------|--------|--------------|------|-------|------|------|--|

| Parameter                       |       | Symbol | Conditions   | Min. | Тур.* | Max. | Sint |  |

| $EXTCLK \to POCLK$              | Delay | tpHL   | CLKSEL = "0" |      | 12.0  |      | ns   |  |

| $EXTCLK \to POCLK$              | Delay | tpHL   | CLKSEL = "0" |      | 12.0  |      | ns   |  |

| $EXTCLK \to DO,  \overline{DO}$ | Delay | tpd    | CLKSEL = "0" |      | 6.0   |      | ns   |  |

\* : Typical values assume that  $V_{CC}$  = +5.0 V and Ta = +25°C.

### (2) MB583A (receiver)

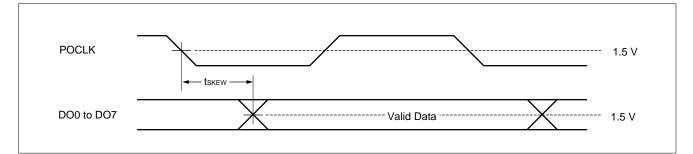

### • Parallel clock output and parallel data output timings

(Vcc = +5.0 V ±5.0 %, Ta = -40°C to +85°C)

| Baram                                                                               | otor      | Symbol        | Conditions        |      | Unit  |      |    |

|-------------------------------------------------------------------------------------|-----------|---------------|-------------------|------|-------|------|----|

| Farain                                                                              | Parameter |               | Symbol Conditions | Min. | Тур.* | Max. |    |

| $\begin{array}{c} \text{POCLK} \rightarrow \text{DO0 to} \\ \text{DO7} \end{array}$ | Skew      | <b>t</b> skew | _                 | -5.0 | 0     | 5.0  | ns |

\* : Typical values assume that  $V_{CC}$  = +5.0 V and Ta = +25°C

#### Reset input pulse width

(Vcc = +5.0 V ±5.0 %, Ta = -40°C to +85°C)

| Parameter |             | Symbol | Conditions                    | Value |      |      | Unit |

|-----------|-------------|--------|-------------------------------|-------|------|------|------|

|           | Falameter   | Symbol | mbol Conditions Min. Typ. Max |       | Max. | Unit |      |

| RESET     | Pulse width | twrst  | _                             | 100   |      |      | ns   |

• External serial clock input timing

(Vcc = +5.0 V ±5.0 %, Ta = -40°C to +85°C)

| Parameter                             |            | Symbol      | Conditions   |      | Unit  |      |      |

|---------------------------------------|------------|-------------|--------------|------|-------|------|------|

|                                       |            | Symbol      | Conditions   | Min. | Тур.* | Max. | Unit |

| $EXTCLK\leftrightarrowD,\overline{D}$ | Setup time | <b>t</b> su | CLKSEL = "0" | 1.5  |       |      | ns   |

|                                       | Hold time  | th          |              | 1.5  |       | _    | ns   |

| EXTCLK → POCLK                        | Delay      | tpHL1       | CLKSEL = "0" |      | 15.0  |      | ns   |

|                                       | Delay      | tpLH2       | CLRSEL = 0   |      | 15.0  |      | ns   |

| EXTCLK $\rightarrow$ DO0 to DO7       | Delay      | tpHL2       | CLKSEL = "0" | _    | 15.0  |      | ns   |

|                                       | Delay      | tpLH2       |              |      | 15.0  |      | ns   |

\* : Typical values assume that  $V_{CC}$  = +5.0 V and Ta = +25°C.

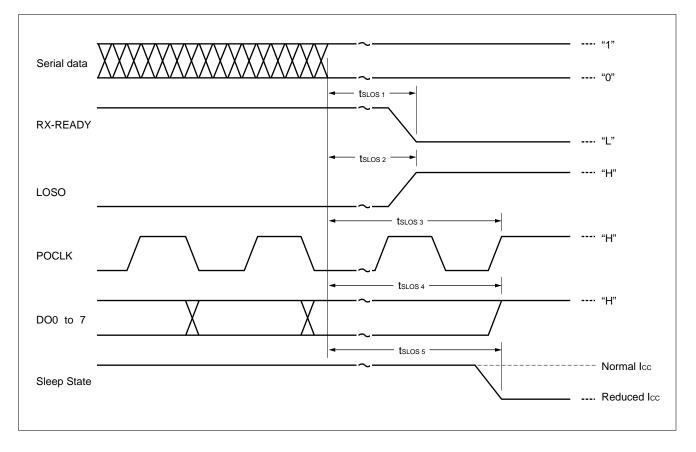

### • Loss-state serial data timing

#### (Vcc = +5.0 V ±5.0 %, Ta = -40°C to +85°C)

| Parameter                                        |       | Symbol | Conditions | Value |       |      | Unit |

|--------------------------------------------------|-------|--------|------------|-------|-------|------|------|

|                                                  |       |        |            | Min.  | Тур.* | Max. | Unit |

| Serial data loss state $\rightarrow$ RX-READY    | Delay | tsLos1 | _          | _     | 2.5   | _    | μs   |

| Serial data loss state $\rightarrow$ LOSO        | Delay | tsLos2 |            | _     | 2.5   |      | μs   |

| Serial data loss state $\rightarrow$ POCLK       | Delay | tsLos3 | _          | _     | 10    |      | μs   |

| Serial data loss state $\rightarrow$ DO0 to DO7  | Delay | tslos4 | _          | _     | 10    |      | μs   |

| Serial data loss state $\rightarrow$ Sleep state | Delay | tslos5 |            |       | 10    |      | μs   |

\* : Typical values assume that V<sub>CC</sub> = +5.0 V and Ta = +25°C.

### • Loss signal timing

| Parameter                             |       | Symbol         | Conditions | Value |       |      | Unit |

|---------------------------------------|-------|----------------|------------|-------|-------|------|------|

|                                       |       |                |            | Min.  | Тур.* | Max. | Unit |

| LOSI, TLOSI<br>$\rightarrow$ RX-READY | Delay | <b>t</b> LOSI1 | —          | _     | 20    |      | ns   |

| LOSI, TLOSI<br>→ LOSO                 | Delay | tLOSI2         | _          | _     | 20    |      | ns   |

| LOSI, TLOSI $\rightarrow$ POCLK       | Delay | <b>t</b> LOSI3 | _          | _     | 7     |      | μs   |

| LOSI, TLOSI $\rightarrow$ DO0 to DO7  | Delay | tLOSI4         | _          | _     | 7     |      | μs   |

| LOSI, TLOSI $\rightarrow$ sleep mode  | Delay | tlosi5         | _          | _     | 7     |      | μs   |

$(V_{CC} = +5.0 \text{ V} \pm 5.0 \text{ \%}, \text{Ta} = -40^{\circ}\text{C to } +85^{\circ}\text{C})$

\* : Typical values assume that Vcc = +5.0 V and Ta = +25°C.

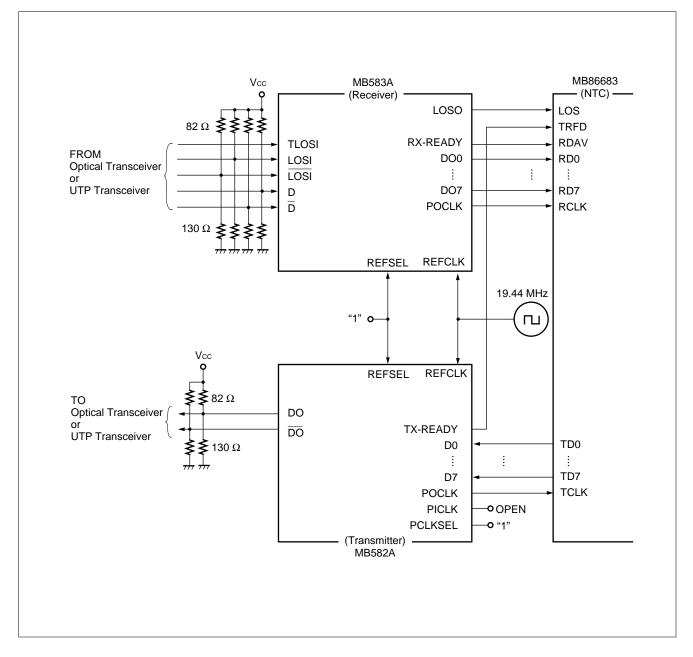

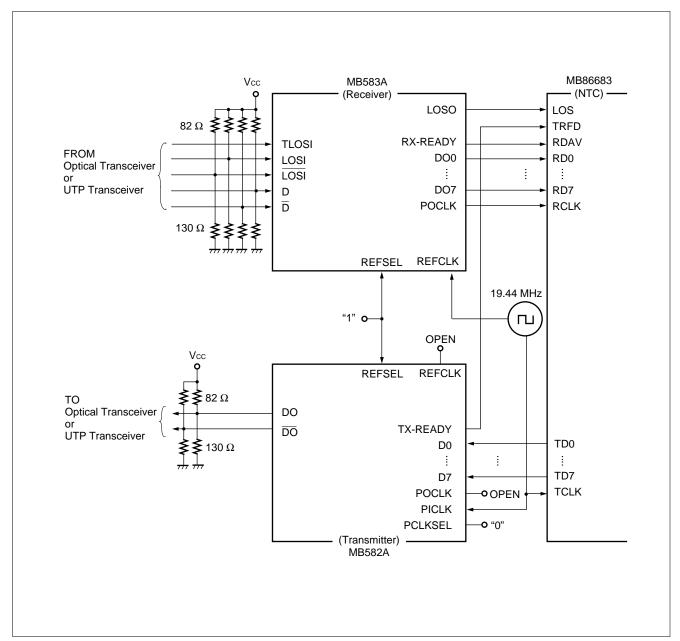

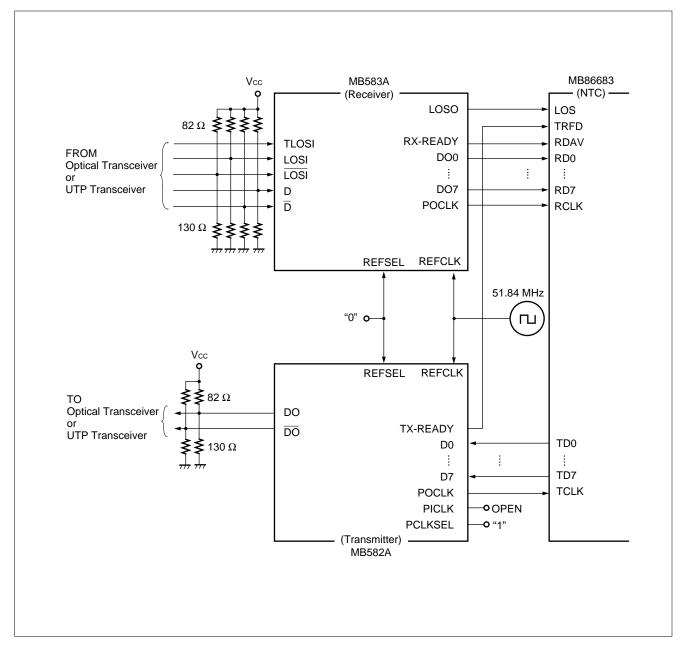

### ■ APPLICATION EXAMPLES

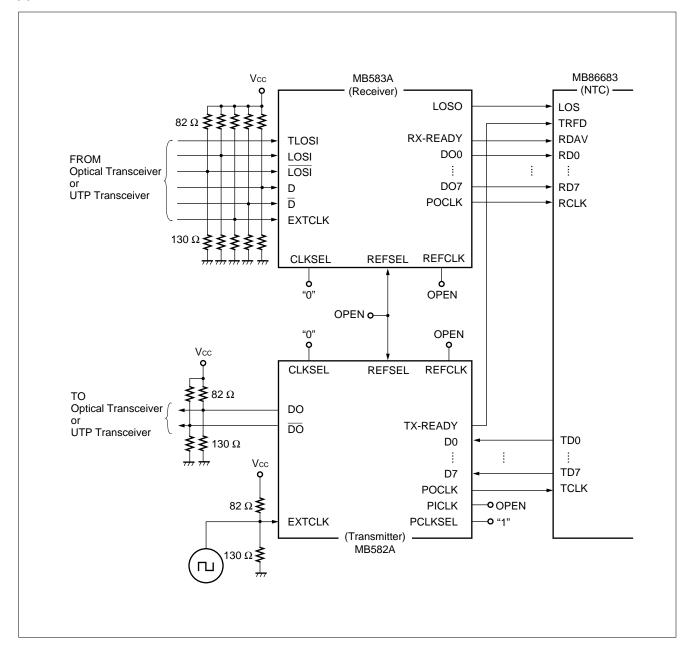

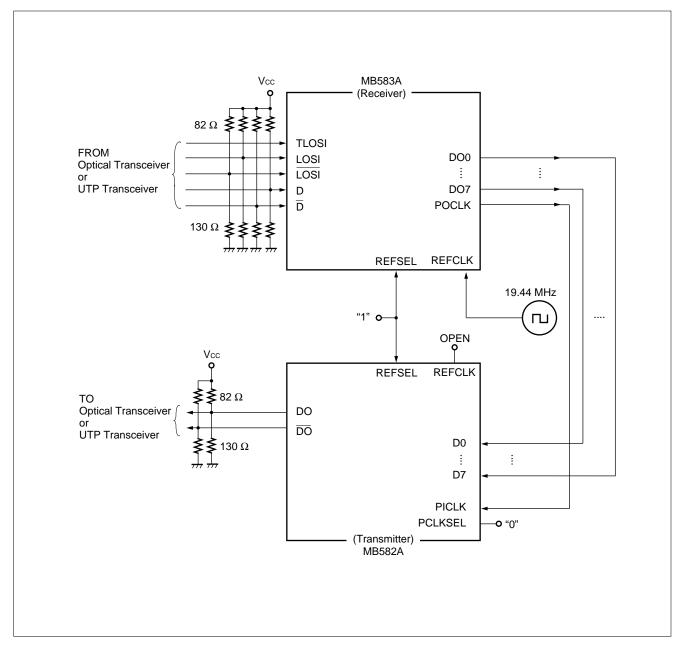

### (1) When REFCLK = 19.44 MHz is used (without PICLK)

(2) When the MB582A uses PICLK = 19.44 MHz (without REFCLK) and the MB583A uses REFCLK = 19.44 MHz

### (3) When REFCLK = 51.84 MHz is used

#### (4) When the external clock is used

### (5) When loopback is used

(6)

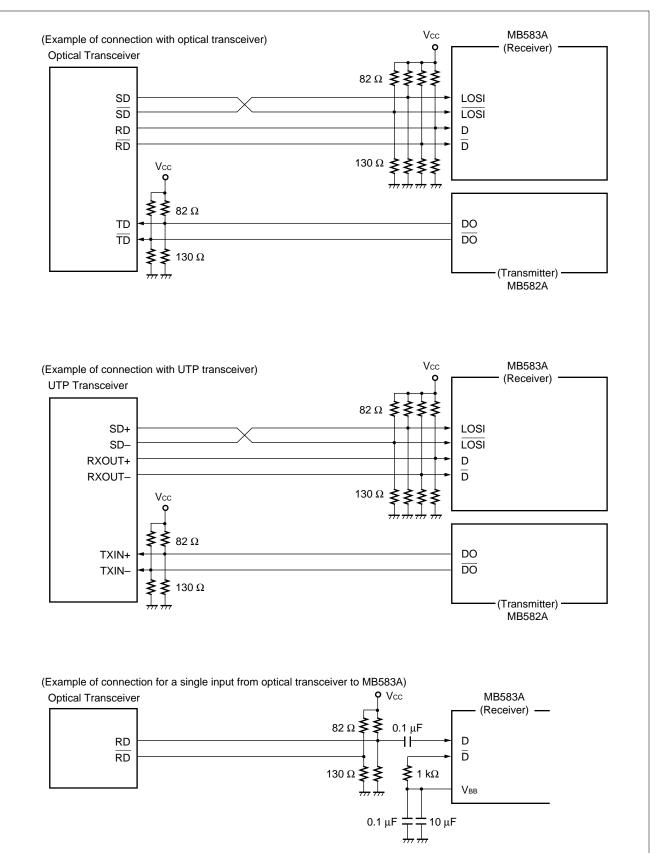

### ■ PERIPHERAL CIRCUITS

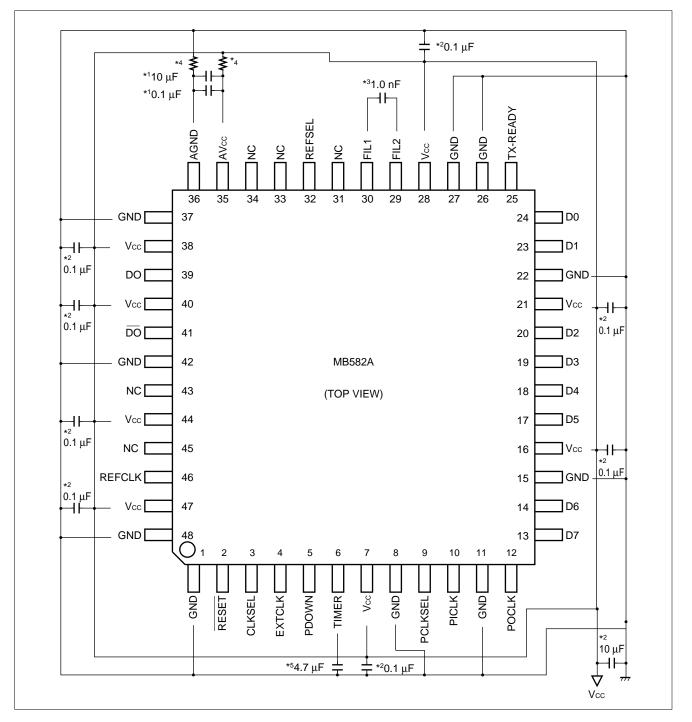

### • MB582A (Transmitter)

\*1: Bypass capacitor for power supply, connected between analog GND and analog  $V_{CC}$ .

\*2: Bypass capacitor for power supply, connected between digital GND and digital Vcc.

\*3: Filter capacitor.

\*4: Although resistance is 0  $\Omega$ , reserve AGND and AV<sub>CC</sub> patterns.

\*5: Capacitor for power-on reset.

Note: External elements should be located as closer to the relevant pins as possible.

• MB583A (Receiver)

\*1: Bypass capacitor for power supply, connected between analog GND and analog Vcc.

\*2: Bypass capacitor for power supply, connected between digital GND and digital Vcc.

\*3: Filter capacitor.

\*4: Although resistance is 0  $\Omega$ , reserve AGND and AVcc patterns.

\*5: Capacitor for power-on reset.

Note: External elements should be located as closer to the relevant pins as possible.

### ■ PRECAUTIONS

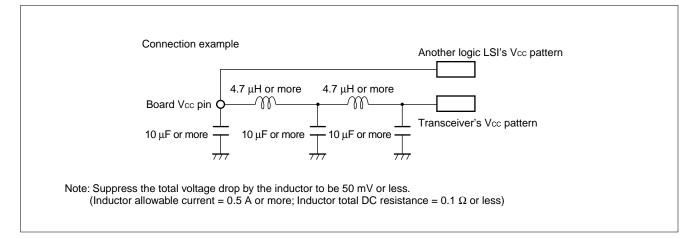

- (1) For the Vcc supplied to the MB582A/583A, use a stable power supply. If spike noise enters the power supply, the MB582A/583A may fail to perform stable operation.

- 1-1. The power supply for this LSI should be separated from the power supply for any other LSI not to receive digital noise (as shown in the following illustration).

- 1-2. To prevent spike noise from another LSIs, add sufficient capacitance also to another LSIs (for example, 10  $\mu$ F for each of the LSIs).

- 1-3. Connect a bypass capacitor of about 0.1  $\mu$ F closer (as within 10 mm as possible) to the pins between each Vcc and GND.

Between AVcc and AGND which are an analog Vcc and an analog GND, in particular, connect a bypass capacitor closer (within 10 mm) to the LSI pins.

For the power source, attach a capacitor with a large value of about 10  $\mu$ F to provide stable power.

- (2) A external filter capacitor between FIL1 and FIL2 must be placed closer (as within 15 mm as possible) to the LSI pins. This capacitor must be wired by minimum routing. The wiring should not cross any other pattern. The pins are particularly sensitive to external noise. Placing this capacitor at lower-noise positions ensure their stable operations. In addition, routing GND patterns around the pins and the capacitor greatly contributes to stable operation.

- (3) Letting the wiring for reference clock signals supplied to the REFCLK and PICLK cross other patterns increases jitter, leading to unstable operation. Note also that input of a reference clock signal with large undershoot results in unstable operation.

- (4) Serial data signals are transmitted at a high speed of 155.52 Mbps. Pay attention to the following points:

- 4-1. Connect a serial data terminal resistor of 82 Ω to the Vcc and of 130 Ω to the GND. Connect these terminal resistors closer to the receiving device side. (Placing a terminal resistor far away from the receiving device causes signal reflection, resulting in degradation of serial data.)

- 4-2. The serial data transmission line must have 50  $\Omega$  impedance. (Inappropriate line impedance causes signal reflection, resulting in degradation of serial data.)

- 4-3. Do not bend the serial data transmission line with 90°. Also, do not pass it through a through hole. (The through hole causes an impedance mismatch.)

- 4-4. The serial data transmission line should be minimum routed.

- (5) Taking account of the above points, the board plane should be a four or more layers.

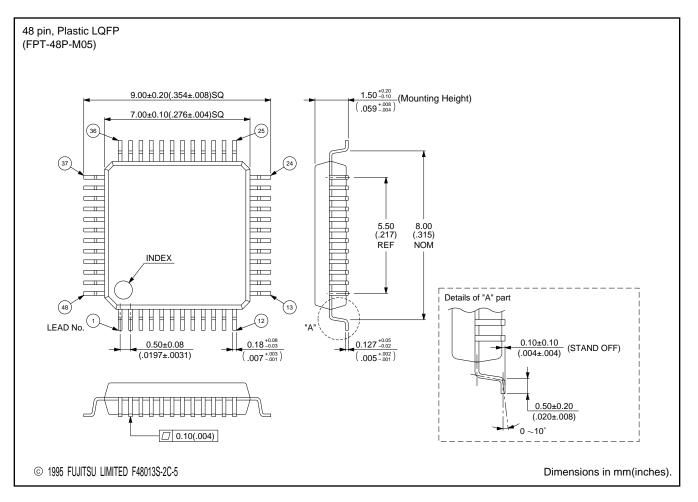

### ■ ORDERING INFORMATION

| Part number | Package             | Remarks |

|-------------|---------------------|---------|

| MB582APFV   | 48 pin Plastic SQFP |         |

| MB583APFV   | (FPT-48P-M05)       |         |

### ■ PACKAGE DIMENSION

### **FUJITSU LIMITED**

For further information please contact:

#### Japan

FUJITSU LIMITED **Corporate Global Business Support Division Electronic Devices** KAWASAKI PLANT, 4-1-1, Kamikodanaka Nakahara-ku, Kawasaki-shi Kanagawa 211-88, Japan Tel: (044) 754-3763 Fax: (044) 754-3329

#### North and South America

FUJITSU MICROELECTRONICS, INC. Semiconductor Division 3545 North First Street San Jose, CA 95134-1804, U.S.A. Tel: (408) 922-9000 Fax: (408) 432-9044/9045

#### Europe

FUJITSU MIKROELEKTRONIK GmbH Am Siebenstein 6-10 63303 Dreieich-Buchschlag Germany Tel: (06103) 690-0 Fax: (06103) 690-122

#### Asia Pacific

FUJITSU MICROELECTRONICS ASIA PTE. LIMITED #05-08, 151 Lorong Chuan New Tech Park Singapore 556741 Tel: (65) 281-0770 Fax: (65) 281-0220

All Rights Reserved.

The contents of this document are subject to change without notice. Customers are advised to consult with FUJITSU sales representatives before ordering.

The information and circuit diagrams in this document presented as examples of semiconductor device applications, and are not intended to be incorporated in devices for actual use. Also, FUJITSU is unable to assume responsibility for infringement of any patent rights or other rights of third parties arising from the use of this information or circuit diagrams.

FUJITSU semiconductor devices are intended for use in standard applications (computers, office automation and other office equipment, industrial, communications, and measurement equipment, personal or household devices, etc.). CAUTION:

Customers considering the use of our products in special applications where failure or abnormal operation may directly affect human lives or cause physical injury or property damage, or where extremely high levels of reliability are demanded (such as aerospace systems, atomic energy controls, sea floor repeaters, vehicle operating controls, medical devices for life support, etc.) are requested to consult with FUJITSU sales representatives before such use. The company will not be responsible for damages arising from such use without prior approval.

Any semiconductor devices have inherently a certain rate of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

If any products described in this document represent goods or technologies subject to certain restrictions on export under the Foreign Exchange and Foreign Trade Control Law of Japan, the prior authorization by Japanese government should be required for export of those products from Japan.